Lauterbach演示了Zynq UltraScale + MPSoC上的ARM Cortex-A53和Cortex-R5內(nèi)核在2015年嵌入式世界中首次使用其TRACE32產(chǎn)品進(jìn)行同步調(diào)試和跟蹤。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

嵌入式

+關(guān)注

關(guān)注

5208文章

20620瀏覽量

336669 -

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133629 -

調(diào)試

+關(guān)注

關(guān)注

7文章

653瀏覽量

35862

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

AMD Zynq UltraScale+ RFSoC評(píng)估套件調(diào)試檢查表

本篇文章包含一份調(diào)試檢查表,它是對(duì) AMD Zynq UltraScale+ RFSoC 評(píng)估套件(ZCU208、ZCU216、ZCU111 和 ZCU670)上評(píng)估板相關(guān)問(wèn)題進(jìn)行故障排除的重要資源。

如何在Zynq UltraScale+ MPSoC平臺(tái)上通過(guò)JTAG啟動(dòng)嵌入式Linux鏡像

流程教程)。本文則進(jìn)一步講解如何在 Zynq UltraScale+ MPSoC 平臺(tái)上通過(guò) JTAG 逐步啟動(dòng) Linux,并提供了完整的過(guò)程與關(guān)鍵命令。只要按步驟操作,即使是復(fù)雜的 Linux 鏡像也能成功通過(guò) JTAG 啟

如何在ZYNQ本地部署DeepSeek模型

一個(gè)將最小號(hào) DeepSeek 模型部署到 AMD Zynq UltraScale+ MPSoC 處理系統(tǒng)的項(xiàng)目。

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

的性能,成為了眾多工程師的首選。本文將深入剖析UltraScale架構(gòu)的各個(gè)方面,為電子工程師們提供全面的技術(shù)參考。 文件下載: AMD ,Xilinx Artix? UltraScale+

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

本教程在 Ubuntu22.04.1 虛擬機(jī)中安裝了 Xilinx 2024.1 的開(kāi)發(fā)環(huán)境,基于該環(huán)境從源碼編譯 PYNQ 3.1.2 工程,生成能夠在 ALINX AXU15EGB 開(kāi)發(fā)板上運(yùn)行的 PYNQ 系統(tǒng)鏡像。

雙Zynq MPSoC PS側(cè)PCIe高速DMA互連解決方案

在涉及Xilinx Zynq UltraScale+ MPSoC的項(xiàng)目中,實(shí)現(xiàn)設(shè)備間高速、低延遲的數(shù)據(jù)傳輸往往是核心需求之一。PCIe(尤其PS側(cè))結(jié)合DMA(直接內(nèi)存訪問(wèn))正是滿足這

AMD Spartan UltraScale+ FPGA的優(yōu)勢(shì)和亮點(diǎn)

AMD Spartan UltraScale+ FPGA 集小型封裝、先進(jìn)的 I/O 功能與低功耗等優(yōu)勢(shì)于一體。該系列 FPGA 配備高速 16.3 Gb/s 收發(fā)器、內(nèi)置的外部?jī)?nèi)存控制器以及

AMD Vivado IP integrator的基本功能特性

我們還將帶您了解在 AMD Zynq UltraScale+ MPSoC 開(kāi)發(fā)板與 AMD Versal 自適應(yīng) SoC 開(kāi)發(fā)板上使用 IP integrator 時(shí),兩種設(shè)計(jì)流程之間存在的差異。

fpga開(kāi)發(fā)板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開(kāi)發(fā)板用戶手冊(cè)

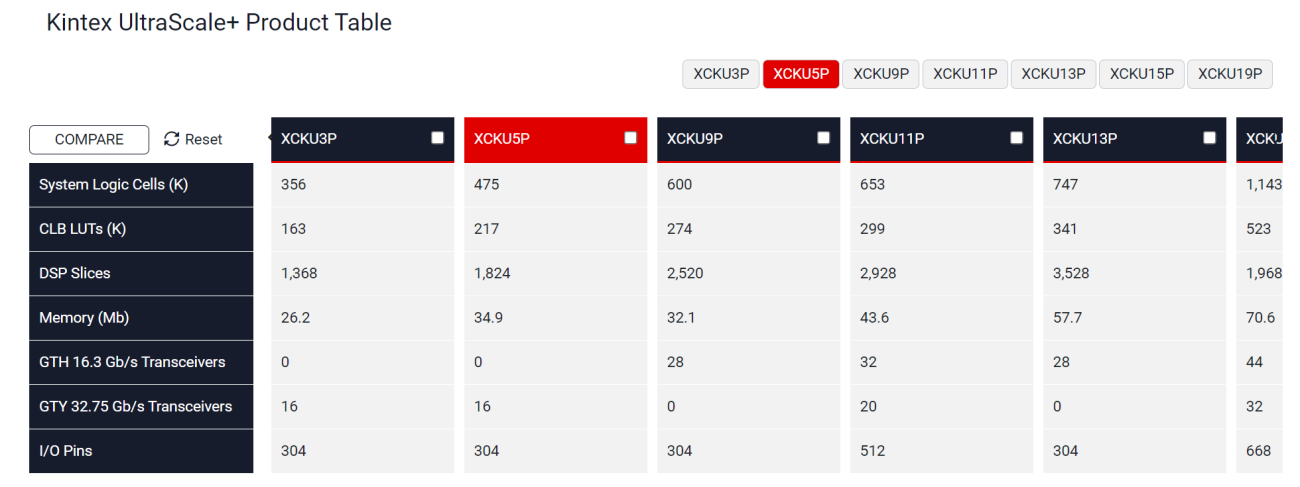

Xilinx Kintex UltraScale+系列FPGA器件采用FinFET工藝,具有120萬(wàn)邏輯單元、UltraRAM、100G以太網(wǎng)MAC等資源,功耗比7系列降低60%。璞致電子開(kāi)發(fā)

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無(wú)線電旗艦開(kāi)發(fā)平臺(tái)

璞致電子 PZ-ZU49DR-KFB 開(kāi)發(fā)板基于 Xilinx ZYNQ UltraScale+ RFSoC XCZU49DR 主控制器,以 "ARM+FPGA 異構(gòu)架構(gòu)" 為

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構(gòu)架構(gòu)下的智能邊緣計(jì)算標(biāo)桿

璞致電子推出PZ-ZU15EG-KFB異構(gòu)計(jì)算開(kāi)發(fā)板,搭載Xilinx ZYNQ UltraScale+ XCZU15EG芯片,整合四核ARM Cortex-A53、雙核Cortex-R5F

AMD FPGA異步模式與同步模式的對(duì)比

本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同步模式的對(duì)比及其對(duì)時(shí)鐘設(shè)置的影響。

AMD Spartan UltraScale+ FPGA 開(kāi)始量產(chǎn)出貨

高 I/O、低功耗及先進(jìn)的安全功能,適用于成本敏感型邊緣應(yīng)用 AMD 很高興宣布,Spartan UltraScale+ 成本優(yōu)化型系列的首批器件現(xiàn)已投入量產(chǎn)! 三款最小型的器件——SU10P

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

。Ultrascale+采用16ns,有3個(gè)系列:Artix,Kintex,Virtex。不僅是工藝制程方面,在其他方面也存在較大改進(jìn),如時(shí)鐘資源與架構(gòu),本文將重點(diǎn)介紹Ultrascale的時(shí)鐘資源與架構(gòu),Ultrascale+

Xilinx Zynq UltraScale+ MPSoC的同步調(diào)試和跟蹤演示

Xilinx Zynq UltraScale+ MPSoC的同步調(diào)試和跟蹤演示

評(píng)論